2025年量子纠错硬件:通向容错量子计算的重要飞跃。探索下一代硬件如何塑造量子可靠性和商业化的未来。

- 执行摘要:2025年量子纠错硬件格局

- 市场规模、增长预测及复合年增长率(2025–2030)

- 主要参与者与行业举措(IBM、谷歌、Rigetti、IonQ、Quantinuum)

- 核心技术:表面码、猫量子比特和拓扑方法

- 硬件架构:超导、离子阱和光子平台

- 集成挑战:可扩展性、保真度和功耗

- 近期突破与演示(2023–2025)

- 商业化路线图:从实验室到市场部署

- 监管、标准化与行业合作(IEEE、QED-C)

- 未来展望:对量子计算和行业应用的影响

- 来源与参考文献

执行摘要:2025年量子纠错硬件格局

量子纠错(QEC)硬件正迅速成为下一代量子计算机的重要推动力,解决量子比特去相干和操作错误的根本挑战。到2025年,该领域由先进材料、新型量子比特架构和集成控制系统的融合所定义,领先的量子硬件公司正在加速实验室演示向可扩展的容错量子处理器的转变。

该领域由少数主要参与者主导,他们各自追求不同的硬件策略。IBM 继续推进其超导量子比特路线图,2025年的系统中集成了硬件高效的表面码实现和支持逻辑量子比特的低温控制电子设备。谷歌 同样专注于超导电路,已展示小规模的表面码补丁,并力求实现误差率低于所谓“盈亏平衡”阈值的逻辑量子比特。Rigetti Computing 和 Quantinuum(霍尼韦尔量子解决方案与剑桥量子合并)也在推动纠错量子硬件的边界,Quantinuum 利用离子阱技术实现实时量子纠错循环,并演示逻辑量子比特的寿命超出物理量子比特的寿命。

与此同时,PsiQuantum 正在追求光子方法,旨在利用硅光子技术和集成错误纠正实现大规模的容错量子计算。他们的硬件路线图强调了在芯片级别集成错误纠正,专注于制造能力和可扩展性。Delft Circuits 和 Qblox 在开发低温和常温控制硬件方面表现突出,这对于QEC协议所需的实时反馈和低延迟操作至关重要。

预计到2025年,整个行业将首次展示逻辑量子比特的寿命和保真度超过其组成的物理量子比特,这一里程碑将验证QEC硬件的实际效用。在接下来的几年里,前景包括逻辑量子比特阵列的扩展、用于错误解码的经典协处理器的集成,以及优化QEC性能的硬件软件协同设计的改进。随着量子硬件的成熟,生态系统可能会看到硬件制造商、控制系统开发者和量子算法专家之间的合作增加,加速通往可商业化的、经过纠错的量子计算的路径。

市场规模、增长预测及复合年增长率(2025–2030)

量子纠错(QEC)硬件市场正势头迅猛,随着量子计算从实验室研究转向早期商业部署,预计将显著扩展。到2025年,全球量子计算硬件市场估计在单数十亿美元的低端,QEC硬件由于其在扩展量子处理器和实现容错中的关键作用,成为快速增长的子集。QEC硬件的需求源于减轻量子比特(qubit)去相干和操作错误的需要,这对实际的量子计算至关重要。

关键行业参与者如IBM、英特尔、Rigetti Computing和Quantinuum正在积极开发集成QEC的硬件架构。例如,IBM已公开承诺在2020年代后期实现大规模的纠错量子系统,其2025年路线图包括逻辑量子比特和硬件嵌入式错误纠正的部署。类似地,Rigetti Computing和Quantinuum分别在推进超导和离子阱平台,专注于可扩展的QEC实现。

QEC硬件细分市场的增长预测表明,在2025年到2030年间,复合年增长率(CAGR)将超过30%,超过更广泛的量子硬件市场。这一加速增长归因于公共和私人对量子基础设施的投资,以及越来越多的认识到强健的错误纠正是商业量子优势的前提。预计到2030年,市场将达到数十亿美元,其中QEC硬件将占据相当大的份额,因更多量子处理器从嘈杂的中间规模量子(NISQ)设备过渡到经过纠错的架构。

除了成熟的参与者,初创公司和专门的硬件供应商也正在进入QEC生态系统,开发低温控制器、高保真的读取系统和定制的错误纠正芯片组。Quantinuum和Rigetti Computing也在与学术界和政府合作伙伴合作,加速QEC硬件的商业化。

展望未来,预计未来几年将进一步将QEC硬件集成到量子计算平台,尤其是在可访问的量子服务和早期企业应用中进行试点部署。随着技术的成熟,QEC硬件市场预计将成为量子计算行业的核心支柱,支撑向容错量子机器的过渡。

主要参与者与行业举措(IBM、谷歌、Rigetti、IonQ、Quantinuum)

量子纠错(QEC)硬件是领先的量子计算公司实现容错量子计算的核心焦点。在2025年,该领域正经历快速进展,关键参与者如IBM、谷歌、Rigetti Computing、IonQ和Quantinuum在研究和硬件开发方面都领先。

IBM 继续在超导量子比特技术上领跑,专注于增加物理量子比特的数量,并将QEC协议直接集成到硬件中。在2024年,IBM实现了其Eagle处理器上实时错误纠正的演示,预计到2025年将在其下一代系统中部署带有主动错误纠正的逻辑量子比特。IBM的路线图包括开发模块化量子处理器,旨在支持表面码纠错并促进逻辑量子比特的构建带有较低错误率。

谷歌正在推进其Sycamore架构,强调实施表面码QEC。近年来,谷歌已展示了逻辑量子比特的稳定性并通过硬件嵌入错误纠正延长了量子比特的寿命。该公司的2025年重点是扩大错误纠正的逻辑量子比特数量并减少所需的QEC开销,旨在在不久的将来实现实际的容错。

Rigetti Computing 也在追求超导量子比特技术,特别强调高效的硬件QEC方案。Rigetti的Aspen系列处理器正在升级以支持实时错误检测和纠正,利用量子比特连接性和读取保真度的改善。该公司正在与研究机构合作,以优化其硬件的QEC代码,力争在2025年展示具有竞争力错误率的逻辑量子比特。

IonQ 利用离子阱技术,这提供了固有的长相干时间和高保真的门操作——这些是QEC的关键优势。IonQ正在开发支持小规模逻辑量子比特实现的硬件架构,并朝着扩展到更大QEC代码的方向努力。该公司的路线图包括将实时反馈和错误跟踪直接集成到其硬件堆栈中,旨在在未来几年展示健壮的逻辑量子比特。

Quantinuum,由霍尼韦尔量子解决方案与剑桥量子合并而成,利用离子阱硬件和先进的QEC算法。Quantinuum的H系列处理器旨在支持拓扑码的实现和实时纠错。该公司正在与行业和学术合作伙伴积极合作,加速硬件嵌入QEC的部署,目标是在2025年展示容错逻辑量子比特。

展望未来,这些行业领导者预计将在QEC硬件方面取得重大进展,专注于增加逻辑量子比特数量、降低错误率以及在硬件层面整合错误纠正协议。他们的集体努力预计将定义未来几年量子计算硬件的轨迹。

核心技术:表面码、猫量子比特和拓扑方法

量子纠错(QEC)硬件是将量子计算机扩展超越嘈杂的中间规模量子(NISQ)时代的关键推动力。到2025年,该领域在核心QEC技术的实施上正经历快速进展,尤其是在表面码、猫量子比特和拓扑方法方面。这些方法正在被领先的量子硬件公司积极开发和测试,各自利用独特的物理平台和工程策略。

表面码仍然是最广泛采用的QEC方案,因为其相对较高的错误阈值和与二维量子比特阵列的兼容性。IBM 已经在其超导量子比特处理器上展示了多次表面码错误纠正,近期的里程碑包括逻辑量子比特的寿命超过物理量子比特。谷歌 同样报告了显著进展,实现了较低的逻辑错误率,并提升了其Sycamore级设备中的物理量子比特数量。这两家公司都瞄准了逻辑量子比特的展示,其错误率低于所谓的“盈亏平衡点”,这是实现容错量子计算的关键步骤。

猫量子比特通过在微波腔内的相干态超位置中对量子信息进行编码,提供了一种可能具有较低硬件开销的QEC替代途径。位于法国的初创公司Alice & Bob在这一方法上处于最前沿,已展示出具有内置错误偏差和自主错误纠正的高效猫量子比特。他们的路线图包括扩展到逻辑量子比特,其误差率与表面码实现相竞争。Quantinuum 也在探索玻色子码和猫量子比特,利用其离子阱硬件进行灵活的QEC实验。

基于马约拉纳零模的拓扑方法承诺能抗辐射噪声。Quantinuum 和 微软 在这一领域是值得注意的参与者。特别是微软在开发使用混合半导体-超导纳米线的拓扑量子比特方面进行了大量投资,目标是展示非阿贝尔统计和拓扑保护的操作。虽然实用的拓扑量子比特仍处于实验阶段,但材料科学和设备制造的最新进展正在加速潜在演示的时间表。

展望未来,预计接下来的几年将进一步将QEC硬件集成到商业量子处理器中,专注于提高逻辑量子比特的保真度和减少资源开销。跨平台的合作和低温控制电子设备的进展,诸如Rigetti Computing和QuTech追求的,将对于扩大QEC架构至关重要。实现实用且硬件高效的量子纠错的竞争愈发激烈,为在2020年代末期首次演示容错量子算法奠定了基础。

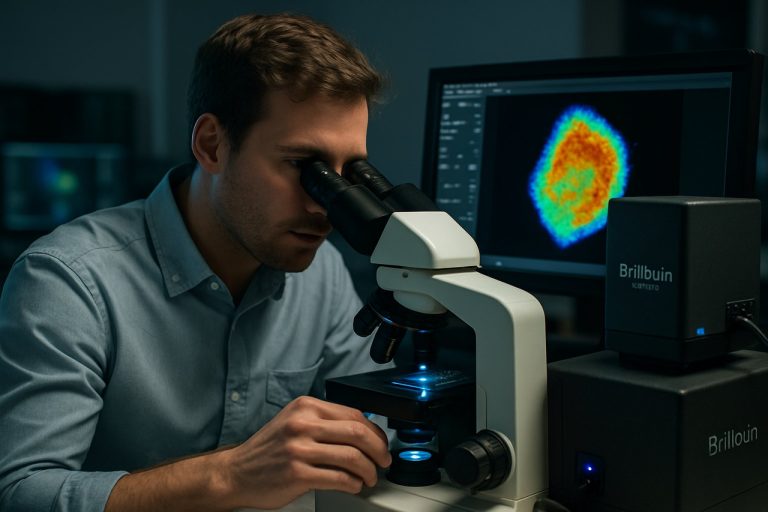

硬件架构:超导、离子阱和光子平台

量子纠错(QEC)硬件是将量子计算机扩展超越嘈杂的中间规模量子(NISQ)时代的关键推动力。到2025年,领先的量子硬件平台——超导量子比特、离子阱和光子系统——都在积极开发和部署QEC方案,每种架构均面临显著的进展和独特挑战。

在超导量子比特系统中,QEC硬件正在迅速推进,受到减轻去相干和门错误需求的驱动。IBM 已在其最新的量子处理器上展示了使用表面码纠错的小型逻辑量子比特操作,并通过可调耦合器及快速高保真读取等硬件改进不断强化性能。谷歌 也报告了逻辑量子比特扩展的进展,专注于增加每个逻辑量子比特的物理量子比特数量和优化低温控制电子设备。这两家公司均以低于物理错误率的逻辑错误率为目标,这是实现容错量子计算的关键里程碑。Rigetti Computing和Quantinuum 也同样在进行硬件级的QEC投资,努力将实时反馈和综合提取直接集成到其控制堆栈中。

由IonQ和Quantinuum领导的离子阱平台,受益于固有的长相干时间和高保真门,这对QEC具有优势。这些公司已经展示了小规模的逻辑量子比特,并正在开发支持模块化扩展和高效综合测量的硬件架构。正在探索分段陷阱和光子互连的使用,以促进大规模QEC所需的并行性。预计在未来几年将部署更大规模的逻辑量子比特阵列,并将QEC例程集成到商业量子云服务中。

以PsiQuantum和Xanadu Quantum Technologies等公司为代表的光子量子计算,正通过玻色子码和簇态架构推动硬件QEC。这些方法利用光子的独特性质,例如低噪声和室温操作,但面临确定性光子生成和抗损失错误纠正的挑战。PsiQuantum正在开发面向大规模QEC的硅光子芯片,目标是实现百万物理量子比特的架构,而Xanadu则在其光子硬件中推进持续变量QEC协议。

在所有平台上,2025年及以后的展望集中于增加逻辑量子比特的规模和可靠性,将QEC集成到硬件和控制系统中,并展示扩展的逻辑量子比特寿命。预计未来几年将展示表现优于其物理对应物的逻辑量子比特,这是实现实用、容错量子计算的重要一步。

集成挑战:可扩展性、保真度和功耗

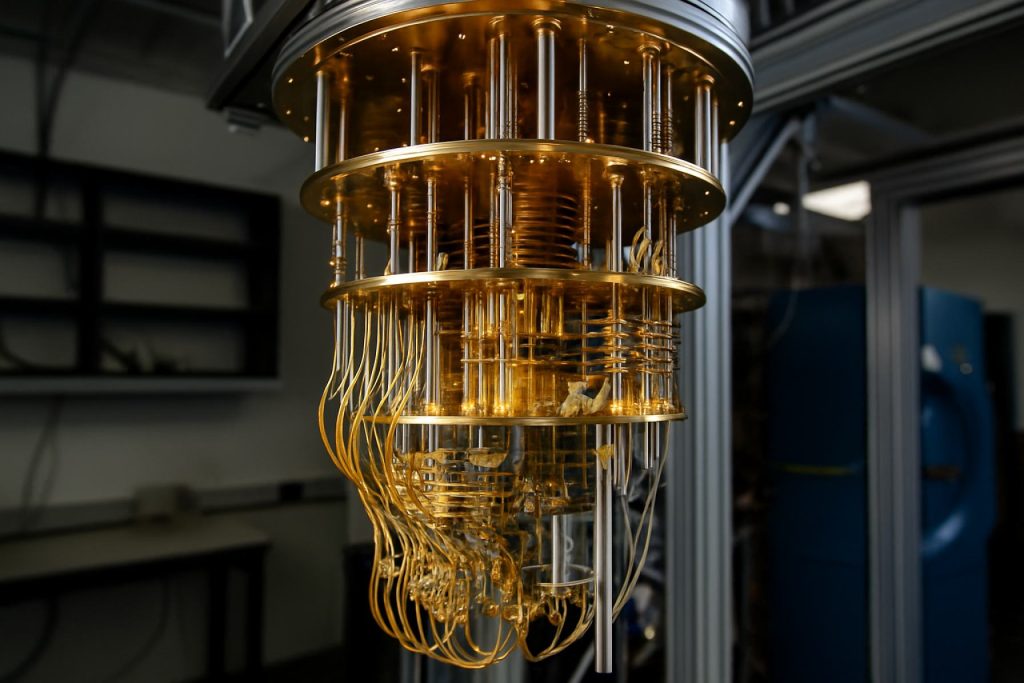

量子纠错(QEC)硬件是构建可扩展、容错量子计算机努力的核心。随着该领域进入2025年,三个主要的集成挑战占据主导地位:可扩展性、保真度和功耗。每个挑战对硬件开发者提出了独特的障碍,影响量子计算的短期发展轨迹。

可扩展性 仍然是一个核心难题。目前的量子处理器,比如由IBM和谷歌开发的,已经展示了拥有超过100个物理量子比特的设备,但QEC需要数千——甚至数百万个物理量子比特才能以足够低的错误率编码一个逻辑量子比特。这个挑战不仅在于制造大规模的量子比特阵列,还在于集成检测和纠正实时错误所需的复杂控制和读取电子设备。像英特尔这样的公司正在探索先进的封装和互连技术,例如3D集成和低温控制芯片,以解决这些扩展瓶颈。

保真度——量子操作的准确性——是另一个关键因素。QEC协议要求门和测量保真度远高于99.9%才有效。尽管IBM和谷歌的超导量子比特平台报告了持续进步,但在大规模、密集打包的量子比特阵列中维持高保真度仍然是一个可怕的挑战。交叉干扰、热噪声和材料缺陷都会降低性能。正在推进的硬件创新,如可调耦合器和改善的量子比特材料,旨在减轻这些影响。Rigetti Computing和Delft Circuits是一些开发新型布线和过滤解决方案,以在规模上保持信号完整性的公司。

功耗越来越被视为一个限制因素,特别是随着系统的增长。QEC硬件必须在毫开尔文的温度下运行,这需要稀释制冷机和专门的低温电子设备。数千个量子比特的控制基础设施可以消耗千瓦的电力,其中很多以热量的形式散发出来,必须从低温环境中去除。英特尔和IBM正在投资于冷CMOS和其他低功耗控制技术,以降低热负荷并推动更大系统的实现。

展望未来,未来几年将继续在材料、器件架构和系统集成方面进行创新。证明逻辑量子比特具有实用误差率的竞赛将推动硬件制造商、组件供应商和研究机构之间的合作。克服这些集成挑战对实现大规模、容错量子计算的承诺至关重要。

近期突破与演示(2023–2025)

在2023到2025年间,量子纠错(QEC)硬件取得了显著进展,数家领先的量子技术公司和研究机构达成了显著里程碑。重点是演示可扩展的、硬件高效的错误纠正方案,并将其集成到越来越复杂的量子处理器中。

2023年,IBM宣布成功演示了使用其超导量子硬件的逻辑量子比特,标志着通向容错量子计算的关键一步。他们的方法利用了表面码错误纠正,在其中将逻辑量子比特编码到物理量子比特的格子中,以允许实时检测和纠正错误。此演示在他们的127量子比特的“Eagle”处理器上进行,随后的迭代提高了逻辑量子比特的保真度和稳定性。

同样,谷歌在实施QEC方面也报告了进展。在2024年,谷歌首次演示了将逻辑错误率抑制在物理错误率以下,这是可扩展量子计算的一个关键阈值。他们的实验使用了重复码和表面码,利用量子比特相干性和门保真度的提升。这些结果得到了同行评议的出版物和公司的公共技术更新的证实。

在离子阱领域,IonQ和Quantinuum均展示了硬件级别的错误纠正。尤其是Quantinuum在其H1系列离子阱处理器上演示了使用Bacon-Shor码实现实时错误检测和纠正循环。他们硬件的全到全连接性和高保真门使得QEC代码的实施更为高效,与某些超导平台相比。

在硬件方面,英特尔和Rigetti Computing等公司已经报告了在低温控制电子设备、量子比特材料和集成错误检测电路方面的进展。英特尔专注于硅自旋量子比特,旨在开发具有内置错误纠正特征的可扩展架构,而Rigetti则展示了在可调耦合器和读取保真度方面的改善,这些都是强健QEC所必需的。

展望未来几年,行业预计QEC硬件将在商业量子处理器中的进一步集成,重点是减少开销并增加逻辑量子比特寿命。改善硬件、实时反馈系统和先进错误纠正代码的融合预计将使实用的容错量子计算更接近现实。

商业化路线图:从实验室到市场部署

量子纠错(QEC)硬件正在迅速从学术原型向商业产品过渡,迫切需要将量子计算机扩展超越嘈杂的中间规模量子(NISQ)时代。到2025年,QEC硬件的商业化路线图受到技术进步和领先量子硬件公司的战略投资的推动,重点是将错误纠正集成到实用的量子处理器中。

QEC硬件所解决的主要挑战是量子比特(qubit)的内在脆弱性,这使其易受去相干和操作错误的影响。为了实现容错量子计算,硬件必须支持逻辑量子比特——这些量子比特通过错误纠正码如表面码编码在多个物理量子比特上。这一需求导致了对可扩展、低噪声量子比特架构和支持控制电子设备的研究与开发激增。

到2025年,IBM继续在QEC硬件集成方面保持领先,已在其超导平台上展示了逻辑量子比特,其错误率低于表面码阈值。其路线图包括部署具有内置错误纠正的模块化量子处理器,目标是在逻辑量子比特操作中首次展示寿命超过最好的物理量子比特。IBM的方案利用先进的低温控制硬件和高保真微波电子设备,专注于将每个逻辑量子比特的物理量子比特数量扩展至数千个。

谷歌同样在推进QEC硬件,其Sycamore及后续处理器的目标是实际算法所需的逻辑量子比特的错误率展示。他们的努力包括开发定制的低温硬件和快速反馈系统,以实现实时的错误检测和纠正。谷歌的路线图预计在接下来的几年内推出第一批错误纠正量子云服务的商业产品,这也依赖于量子比特相干性和门保真度的持续改善。

其他主要参与者如Rigetti Computing,正在开发集成QEC的模块化超导架构,而IonQ则探索具有全到全连接性的离子阱系统,以便高效错误纠正。两家公司都瞄准在2020年代末启动QEC-enabled量子处理器的商业化部署,供云访问和专门应用使用。

展望未来,QEC硬件的商业化将取决于物理量子比特错误率的进一步降低、低温和控制基础设施的改进以及可扩展架构的发展。行业路线图表明,到2020年代末,主动错误纠正的早期商业量子计算机将面世,能够在如密码学、材料科学和优化等领域实现首个容错量子应用。

监管、标准化与行业合作(IEEE、QED-C)

量子纠错(QEC)硬件正迅速成为量子计算行业的一个关键焦点,随着该领域逐步走向实用部署,监管、标准化和协作努力也在加速。到2025年,该领域受到了领先行业财团、标准机构和硬件制造商之间相互作用的影响,所有这些都旨在确保QEC解决方案的互操作性、可靠性和可扩展性。

IEEE在标准化量子技术方面发挥了核心作用,包括错误纠正硬件。IEEE量子倡议通过其量子标准工作组,正在积极制定QEC硬件接口、基准和性能指标的框架和指南。这些努力旨在促进跨平台兼容性,加速QEC在商业量子处理器中的采用。预计IEEE的标准将在未来几年影响量子硬件的采购和监管要求。

另一个主要力量是量子经济发展财团(QED-C),该财团汇聚了来自行业、学术界和政府的利益相关者。QED-C的硬件技术顾问委员会正在努力确定QEC硬件的最佳实践和前竞争标准,重点关注错误率、容错阈值及其与控制电子设备的集成。该财团在2025年的协作项目包括对QEC模块的循环基准测试以及对综合提取电路的开放参考设计开发。

在制造商方面,像IBM、Rigetti Computing和Quantinuum等公司正在积极参与这些标准化工作。以IBM为例,其为错误纠正协议和硬件抽象层的定义作出了贡献,利用其在超导量子比特架构方面的经验。Rigetti正在协作制定硬件-软件共同设计标准,而Quantinuum则根据其离子阱QEC的实施提供了意见。这些公司还在其下一代量子处理器中进行遵循新兴标准的试点,力争在2020年代末展示容错操作。

展望未来,美国、欧盟和亚洲的监管机构预计将在其对量子硬件采购和认证的指导中参考IEEE和QED-C标准。这将进一步推动行业的协调,减少碎片化,并支持QEC组件的强大供应链的发展。随着量子纠错硬件从实验室原型转向商业部署,标准机构与行业财团的合作将对确保量子计算系统的可靠性和可扩展性至关重要。

未来展望:对量子计算和行业应用的影响

量子纠错(QEC)硬件在量子计算演变中将起到变革性作用,特别是随着行业逐步接近实际容错量子系统的门槛。到2025年,领先的量子硬件开发者正在加倍努力,以在物理层面集成QEC,旨在减轻去相干和操作错误,这些限制了量子处理器的可扩展性和可靠性。

主要参与者如IBM、英特尔和Rigetti Computing正在积极开发支持逻辑量子比特的硬件架构——这是实施像表面码这样的QEC代码的必要步骤。在2024年,IBM演示了一款127量子比特的Eagle处理器,并勾勒了错误纠正量子操作的路线图,目标是在2025年部署逻辑量子比特。英特尔正在追求硅自旋量子比特,利用其半导体制造专业知识提高量子比特的一致性和错误率,而Rigetti Computing继续改进其具备集成QEC协议的超导量子比特平台。

同时,硬件创新正在由专注于低温控制电子设备和可扩展互连的公司推动,比如Teledyne Technologies和罗德与施瓦茨。这些公司正在开发高保真信号生成和读取系统,这对QEC所需的实时反馈回路至关重要。此外,Quantinuum(由霍尼韦尔量子解决方案与剑桥量子合并而成)也在推进集成错误纠正的离子阱硬件,最近演示了具有改进寿命和门保真度的逻辑量子比特操作。

展望未来几年,行业预计将首次演示使用QEC硬件保护的逻辑量子比特进行的小规模容错量子计算。这一里程碑预计将解锁新的行业应用,特别是在高度依赖精密模拟的领域,如制药、材料科学和密码学。由于供应商如IBM和Quantinuum准备为商业和研究用户提供访问逻辑量子比特的服务,嘈杂的中间规模量子(NISQ)设备向经过纠错的量子处理器的转变也将催化量子云服务的发展。

总之,2025年对QEC硬件来说是关键的一年,预计在设备级别集成错误纠正方面将取得重大进展。由此带来的量子比特保真度和计算可靠性的改善将加速量子计算在多个行业的接受,为首个实用的大规模量子应用奠定基础。

来源与参考文献

- IBM

- 谷歌

- Rigetti Computing

- Quantinuum

- Qblox

- IonQ

- Alice & Bob

- Quantinuum

- 微软

- Xanadu量子技术

- IBM

- 谷歌

- Rigetti Computing

- IonQ

- Quantinuum

- IEEE

- 量子经济发展财团(QED-C)

- Teledyne Technologies

- 罗德与施瓦茨