Hur staplade CMOS-bildsensorer omdefinierar kamerateknik: Låser upp oöverträffad hastighet, klarhet och miniaturisering för nästa generations enheter

- Introduktion: Vad är staplade CMOS-bildsensorer?

- Hur staplad arkitektur skiljer sig från traditionella CMOS-sensorer

- Genombrott i bildkvalitet och bearbetningshastighet

- Påverkan på smartphone- och konsumentelektronik-kameror

- Möjliggör avancerade funktioner: Högt dynamiskt omfång, prestanda i svagt ljus och AI-integration

- Tillverkningsutmaningar och branschens antagande

- Framtida trender: Bortom smartphones—fordon, säkerhet och industriella tillämpningar

- Slutsats: Vägen framåt för staplade CMOS-bildsensorer

- Källor & Referenser

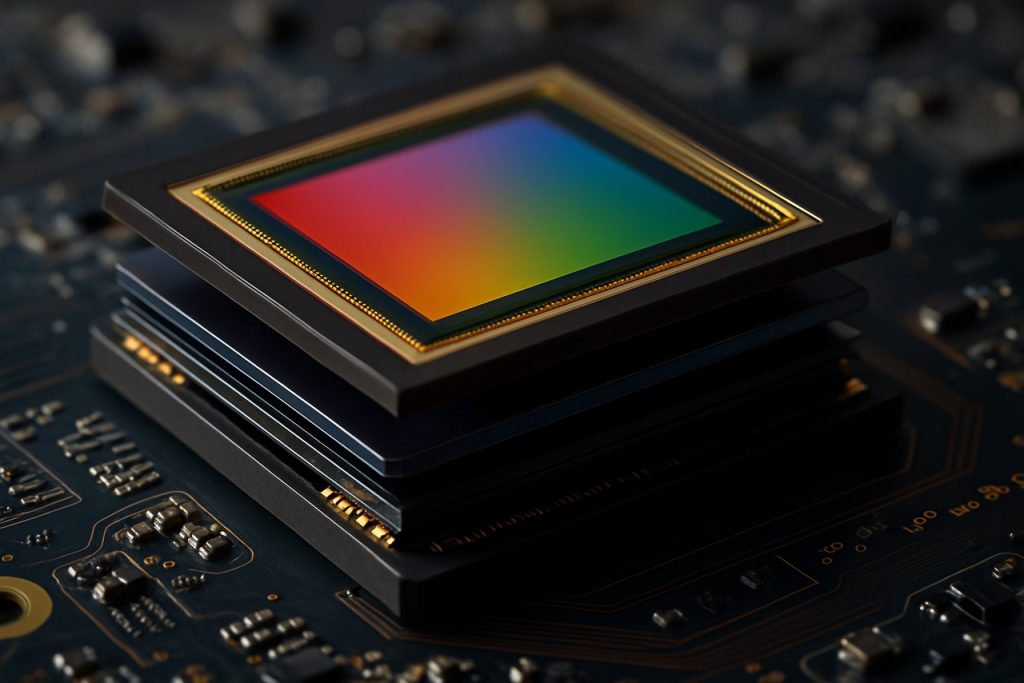

Introduktion: Vad är staplade CMOS-bildsensorer?

Staplade CMOS-bildsensorer representerar ett signifikant framsteg inom digital bildteknik och erbjuder förbättrad prestanda och nya funktioner jämfört med traditionella CMOS-sensorer. I en konventionell CMOS-bildsensor tillverkas fotodioderna och pixelkretsarna på en enda kiselsubstrat. I kontrast separerar staplade CMOS-bildsensorer pixel- och logiklagret (där signalbehandling sker), staplar dem vertikalt och ansluter dem med hjälp av avancerade tekniker som genom-kisel-vior (TSV). Denna arkitektur möjliggör att varje lager kan optimeras oberoende, vilket leder till förbättrad bildkvalitet, snabbare avläsningshastigheter och minskad chipstorlek.

Separeringen av pixel- och logiklager möjliggör integration av mer sofistikerade bearbetningskretsar, såsom hög hastighet analog-till-digitalomvandlare och avancerade brusreduceringsalgoritmer, direkt under pixelarrayen. Detta förbättrar inte bara sensorens dynamiska omfång och prestanda i svagt ljus, utan möjliggör också nya funktioner som realtids HDR-bildtagning och AI-bearbetning på chipet. Staplade CMOS-sensorer används nu i stor utsträckning i smartphones, digitalkameror och fordonsapplikationer, där kompakt storlek och hög prestanda är kritiska krav.

Utvecklingen och kommersialiseringen av staplade CMOS-bildsensorer har drivits av ledande halvledarföretag, där Sony Semiconductor Solutions banar väg för teknologin. När efterfrågan på högre upplösning och smartare bildsystem fortsätter att öka, förväntas staplade CMOS-bildsensorer spela en central roll i utvecklingen av digital bildteknik.

Hur staplad arkitektur skiljer sig från traditionella CMOS-sensorer

Staplade CMOS-bildsensorer representerar en betydande evolution från traditionella CMOS-sensorarkitekturer, främst genom deras innovativa användning av vertikalt integrerade lager. I konventionella CMOS-sensorer finns all pixelkretsning—inklusive fotodioder och signalbehandlingskomponenter—på en enda kiselsubstrat. Denna monolitiska metod förhindrar pixelstorlek, prestanda och integration av avancerade funktioner på grund av utrymme- och processbegränsningar.

I kontrast separerar staplade CMOS-bildsensorer pixelarrayen och logikkretsarna i distinkta lager, som sedan binds samman med avancerade wafer-stapling-tekniker. Det övre lagret innehåller typiskt fotodioderna och färgfilter, som är optimerade enbart för ljusupptagning, medan det nedre lagret rymmer komplexa signalbearbetningskretsar, minne och ibland till och med AI-acceleratorer. Denna separation gör det möjligt för varje lager att tillverkas med processer som bäst passar deras funktion, vilket möjliggör mindre pixlar, högre upplösning och snabbare avläsningshastigheter utan att kompromissa med bildkvalitet eller sensors storlek.

Den staplade arkitekturen underlättar också integration av ytterligare funktioner som AI-fasdetektering, HDR-bearbetning och realtids brusreducering, vilket är utmanande att implementera i traditionella designer. Dessutom, genom att minska ledningar och anslutningslängd mellan pixel- och logiklager, uppnår staplade sensorer lägre strömförbrukning och förbättrad signalintegritet, vilket resulterar i bättre prestanda i svagt ljus och snabbare dataöverföringshastigheter. Ledande tillverkare som Sony Semiconductor Solutions har banat väg för denna teknologi och gjort staplade CMOS-sensorer till hörnstenen i moderna smartphones och digitalkameror.

Genombrott i bildkvalitet och bearbetningshastighet

Staplade CMOS-bildsensorer har drivit på betydande framsteg inom både bildkvalitet och bearbetningshastighet, vilket fundamentalt förändrar digital bildtagning. Genom att vertikalt integrera pixel- och logikkretsarna på separata substrat möjliggör staplade arkitekturer användningen av avancerad signalbearbetning och minne direkt under fotodioderna. Denna separation möjliggör större och mer effektiva pixlar, vilket förbättrar ljuskänslighet och dynamiskt omfång, vilket resulterar i klarare bilder med minskat brus, särskilt i svaga ljusförhållanden. Till exempel har implementeringen av staplad sensor teknologi i konsumentenheter lett till märkbara förbättringar i färgnoggrannhet och detaljbevarande, som demonstreras av Sony Semiconductor Solutions Corporation.

Bearbetningshastigheten har också sett anmärkningsvärda vinster. Den staplade designen möjliggör integration av hög hastighet DRAM eller avancerade logikkretsar direkt under pixelarrayen, vilket möjliggör snabb dataavläsning och realtids bildbehandling. Denna arkitektur stödjer funktioner som ultrav snabbt autofokus, hög bildfrekvens videoskapande och minskad rullande skakningsdistorsion. Till exempel har användningen av staplade sensorer i smartphones och professionella kameror möjliggjort burst-fotografering i hastigheter som tidigare var omöjliga med traditionella CMOS-sensorer, som framhävs av Canon Inc.. Dessutom minskar förmågan att bearbeta bilddata på chipet latens och strömförbrukning, vilket är kritiskt för mobila och inbyggda applikationer.

Sammanfattningsvis representerar staplade CMOS-bildsensorer ett steg framåt inom både bildkvalitet och bearbetningshastighet, vilket banar väg för nya bildbehandlingsapplikationer inom områden som sträcker sig från konsumentelektronik till fordons- och industriella visionssystem.

Påverkan på smartphone- och konsumentelektronik-kameror

Staplade CMOS-bildsensorer har signifikant förändrat landskapet för smartphone- och konsumentelektronik-kameror genom att möjliggöra högre prestanda i allt mer kompakta enheter. Till skillnad från traditionella sensorer separerar staplade CMOS-designs pixelarrayen och logik-kretsarna i olika lager, som sedan vertikalt integreras. Denna arkitektur möjliggör mer avancerad signalbehandling, snabbare avläsningshastigheter och integration av ytterligare funktioner direkt på sensorchipet. Som ett resultat kan smartphones utrustade med staplade CMOS-sensorer uppnå högre upplösning, förbättrad lågljusprestanda och snabbare autofokus, allt inom de slanka former som moderna konsumentenheter kräver.

Effekten av staplade CMOS-sensorer är särskilt tydlig i flaggskeppssmartphones, där tillverkare utnyttjar denna teknologi för att leverera funktioner som realtids HDR, flermärkes brusreducering och videoinspelning i hög hastighet. Till exempel har antagandet av staplad sensorteknik möjliggjort burst-fotografering med upp till 20 bilder per sekund och 4K-videoinspelning vid höga bildfrekvenser, kapabiliteter som tidigare var begränsade till dedikerade kameror. Dessutom minskar den ökade bearbetningskraften på själva sensorn belastningen på huvudapplikationsprocessorn, vilket leder till mer effektiv strömförbrukning och längre batteritid—en avgörande faktor för mobila enheter.

Stora aktörer inom branschen, inklusive Sony Semiconductor Solutions och Samsung Semiconductor, har varit i framkant av utvecklingen av staplade CMOS-sensorer och drivit innovation inom beräkningsfotografi och möjliggjort nya användarupplevelser som avancerade porträttlägen och AI-drivna scenidentifiering. När konsumenternas förväntningar på kameraprestanda fortsätter att öka, är staplade CMOS-bildsensorer beredda att förbli en hörnstensteknologi i utvecklingen av mobila och konsumentbildenheter.

Möjliggör avancerade funktioner: Högt dynamiskt omfång, prestanda i svagt ljus och AI-integration

Staplade CMOS-bildsensorer har revolutionerat kapabiliteterna hos moderna bildbehandlingssystem genom att möjliggöra avancerade funktioner som högt dynamiskt omfång (HDR), överlägsen lågljusprestanda och sömlös integration av AI-bearbetning. Den staplade arkitekturen separerar pixelarrayen och logik-kretsarna i olika lager, som är sammankopplade genom högdensitets vertikala anslutningar. Denna design möjliggör inkluderingen av mer sofistikerad signalbearbetning och minne direkt under pixel-lagret, utan att öka sensorens fotavtryck.

För HDR-bildtagning kan staplade sensorer fånga flera exponeringar samtidigt eller i snabb följd, tack vare den snabba avläsningen som möjliggörs av det dedikerade logiklagret. Detta resulterar i bilder med större detaljrikedom i både ljusa och mörka områden, vilket överträffar kapabiliteterna hos traditionella enskiktsensorer. Förbättrad lågljusprestanda uppnås genom att optimera pixelstrukturen och minska brus genom bearbetning på chipet, vilket är mer genomförbart i en staplad konfiguration. Närheten av avancerade analog-till-digital-omvandlare och brusreduceringskretsar till pixel-lagret minimerar signalförlust, vilket leder till klarare bilder i utmanande ljusförhållanden.

Dessutom, integrationen av AI-acceleratorer inom logiklagret i staplade CMOS-sensorer möjliggör realtids analys av bilder, såsom objektidentifiering, scenigenkänning och autofokusjusteringar, direkt på sensorn. Detta minskar inte bara latens utan avlastar också bearbetningen från huvudprocessorn, vilket möjliggör smartare och mer effektiva bildbehandlingsapplikationer. Ledande tillverkare som Sony Semiconductor Solutions och Samsung Semiconductor har demonstrerat dessa framsteg och satt nya standarder för mobil-, fordons- och industriella bildsystem.

Tillverkningsutmaningar och branschens antagande

Tillverkningen av staplade CMOS-bildsensorer presenterar unika utmaningar jämfört med traditionella fram- eller baksidesbelysta CMOS-sensorer. Staplade arkitekturer kräver exakt anpassning och bindning av flera kiselwafers—som typiskt separerar pixelarrayen från logikkretsarna. Denna process, känd som wafer-till-wafer eller die-till-wafer-bindning, kräver sub-mikron noggrannhet för att säkerställa elektrisk anslutning och bildkvalitet. Att uppnå sådan precision i stor skala ökar komplexiteten och kostnaden, eftersom även minor misalignments kan leda till yield-förlust eller försämrad sensorprestanda. Dessutom introducerar tunnandet av wafers för att möjliggöra stapling en bräcklighet, vilket kräver avancerade hanterings- och inspektionstekniker genom hela produktionslinjen.

En annan betydande utmaning är termisk hantering. Den nära närheten av logik- och pixel-lager kan leda till lokal uppvärmning, vilket potentiellt påverkar sensorbrus och tillförlitlighet. Tillverkare måste därför integrera effektiva lösningar för värmeavledning utan att kompromissa med den kompaktitet som staplade designer erbjuder. Dessutom lägger integrationen av genom-kisel-vior (TSV) för vertikala anslutningar ytterligare processsteg och kräver noggrann optimering för att undvika crosstalk och upprätthålla signalintegritet.

Trots dessa hinder har branschens antagande av staplade CMOS-bildsensorer accelererat, drivet av efterfrågan på högre prestanda i kompakta enheter som smartphones och fordonskameror. Ledande företag som Sony Semiconductor Solutions Corporation och Samsung Electronics har pionjärar massproduktion, vilket utnyttjar proprietära bindande och miniaturiseringstekniker. När tillverkningsteknikerna mognar och stordriftsfördelar förbättras förväntas staplade CMOS-sensorer bli standarden för högpresterande bildtillämpningar och ytterligare driva gränserna för sensorprestanda och enhetsintegration.

Framtida trender: Bortom smartphones—fordon, säkerhet och industriella tillämpningar

Staplade CMOS-bildsensorer, som ursprungligen utvecklades för att möta de krävande kraven inom smartphone-fotografi, är nu beredda att revolutionera en rad industrier bortom konsumentelektronik. Inom fordonssektorn integreras dessa sensorer i avancerade förarassistanssystem (ADAS) och autonoma fordon, där deras höga dynamiska omfång, låga brus och snabba avläsningsmöjligheter möjliggör mer pålitlig objektidentifiering och situationsmedvetenhet under utmanande ljusförhållanden. Ledande fordonsleverantörer samarbetar redan med sensortillverkare för att utveckla skräddarsydda staplade CMOS-lösningar för övervakning i bilen och surround-view-system (Sony Semiconductor Solutions Corporation).

Inom säkerhet och övervakning erbjuder staplade CMOS-sensorer betydande fördelar, såsom förbättrad lågljusprestanda och snabbare bildfrekvenser, som är kritiska för realtidsövervakning och ansiktsigenkänning. Förmågan att integrera AI-bearbetning på chipet inom sensorstacken ökar deras användbarhet, vilket möjliggör kantanalys och minskar behovet av högbandwidth dataöverföring till centrala servrar (ams OSRAM).

Industriella tillämpningar drar också nytta av utvecklingen av staplad CMOS-teknologi. Inom maskinsyn, robotik och kvalitetskontroll erbjuder dessa sensorer högre upplösning och snabbare dataflöde, vilket stödjer mer precisa inspektions- och automatiseringsuppgifter. Trenden mot miniaturisering och integration av ytterligare funktioner—som djupmätning och spektralbildtagning—inom sensorstacken förväntas driva ytterligare antagande inom dessa sektorer (onsemi).

När staplade CMOS-bildsensorer fortsätter att utvecklas, förväntas deras påverkan att expandera långt bortom smartphones, vilket möjliggör smartare, säkrare och mer effektiva system inom fordons-, säkerhets- och industriella domäner.

Slutsats: Vägen framåt för staplade CMOS-bildsensorer

Staplade CMOS-bildsensorer har snabbt utvecklats från ett nytt koncept till en hörnstensteknologi i moderna bildsystem. Deras lagerarkitektur, som separerar fotodioden och kretsar i distinkta nivåer, har möjliggjort betydande framsteg inom pixelminiaturisering, avläsningshastighet och energieffektivitet. När efterfrågan på högpresterande bildtagning i smartphones, fordonsystem och industriella tillämpningar fortsätter att öka, är staplade CMOS-sensorer beredda att spela en ännu mer avgörande roll i framtiden för digital bildteknik.

Ser man framåt, är pågående forskning fokuserad på att ytterligare minska pixelstorleken samtidigt som känsligheten och det dynamiska omfånget bibehålls eller förbättras. Innovationer som integration av AI-bearbetning direkt i sensorstacken och användningen av avancerade material för ökad kvanteffektivitet är på horisonten. Dessa utvecklingar lovar att låsa upp nya funktioner, såsom realtidsberäkningsfotografi och avancerade maskinsynsfunktioner, direkt på sensor-nivå.

Dock kvarstår utmaningar, inklusive komplexiteten i att tillverka flerskiktade strukturer och säkerställa hög utbyte och tillförlitlighet i stor skala. Branschledare investerar i nya tillverkningstekniker och designmetoder för att ta itu med dessa hinder. När dessa teknologier mognar, förväntas staplade CMOS-bildsensorer bli ännu mer spridda, vilket driver nästa våg av innovation inom bildtagning över olika sektorer. För en omfattande översikt av nuvarande trender och framtida riktningar, se resurser från Sony Semiconductor Solutions Corporation och Canon Inc..