Hardware de Correção de Erros Quânticos em 2025: O Salto Crítico Rumo à Computação Quântica Tolerante a Falhas. Explore Como o Hardware de Próxima Geração Está Moldando o Futuro da Confiabilidade Quântica e Comercialização.

- Resumo Executivo: Paisagem de Hardware de Correção de Erros Quânticos 2025

- Tamanho do Mercado, Previsões de Crescimento e CAGR (2025–2030)

- Principais Jogadores e Iniciativas da Indústria (IBM, Google, Rigetti, IonQ, Quantinuum)

- Tecnologias Centrais: Códigos de Superfície, Qubits Gato e Abordagens Topológicas

- Arquiteturas de Hardware: Supercondutores, Íons Aprisionados e Plataformas Fotônicas

- Desafios de Integração: Escalabilidade, Fidelidade e Consumo de Energia

- Avanços Recentes e Demonstrações (2023–2025)

- Roteiro de Comercialização: Do Laboratório à Implantação no Mercado

- Regulamentação, Padronização e Colaboração na Indústria (IEEE, QED-C)

- Perspectivas Futuras: Impacto na Computação Quântica e Aplicações da Indústria

- Fontes e Referências

Resumo Executivo: Paisagem de Hardware de Correção de Erros Quânticos 2025

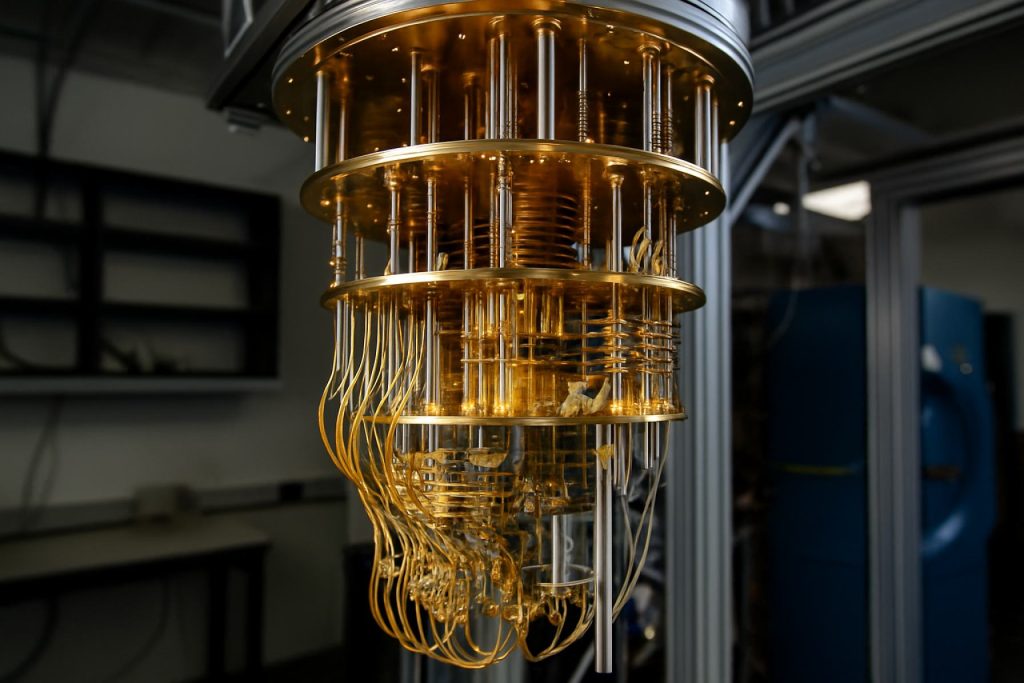

O hardware de correção de erros quânticos (QEC) está rapidamente se destacando como um habilitador crítico para a próxima geração de computadores quânticos, abordando o desafio fundamental da decoerência de qubits e erros operacionais. Em 2025, a paisagem é definida por uma convergência de materiais avançados, novas arquiteturas de qubits e sistemas de controle integrados, com as principais empresas de hardware quântico acelerando a transição de demonstrações laboratoriais para processadores quânticos escaláveis e tolerantes a falhas.

O campo é dominado por um punhado de grandes jogadores, cada um perseguindo estratégias de hardware distintas. IBM continua a avançar em seu roteiro de qubits supercondutores, com seus sistemas de 2025 incorporando implementações de código de superfície eficientes em hardware e eletrônicos de controle criogênico projetados para suportar qubits lógicos. Google está igualmente focada em circuitos supercondutores, tendo demonstrado pequenos patches de código de superfície e visando a realização de qubits lógicos com taxas de erro abaixo do chamado limite de “break-even”. Rigetti Computing e Quantinuum (uma fusão da Honeywell Quantum Solutions e Cambridge Quantum) também estão empurrando as fronteiras do hardware quântico corrigido por erros, com a Quantinuum aproveitando a tecnologia de íons aprisionados para implementar ciclos de QEC em tempo real e demonstrar tempos de vida de qubits lógicos que superam os qubits físicos.

Em paralelo, a PsiQuantum está buscando uma abordagem fotônica, visando aproveitar a fotônica de silício e a correção de erros integrada para alcançar a computação quântica tolerante a falhas em grande escala. Seu roteiro de hardware enfatiza a integração da correção de erros no nível do chip, com foco na fabricabilidade e escalabilidade. Delft Circuits e Qblox são notáveis pelo seu desenvolvimento de hardware de controle criogênico e em temperatura ambiente, que é essencial para o feedback em tempo real e operações de baixa latência exigidas pelos protocolos de QEC.

Setorialmente, espera-se que 2025 veja as primeiras demonstrações de qubits lógicos com tempos de vida e fidelidades que superam os de seus qubits físicos constituintes, um marco que validará a utilidade prática do hardware de QEC. As perspectivas para os próximos anos incluem a ampliação de matrizes de qubits lógicos, a integração de coprocessadores clássicos para decodificação de erros e o aprimoramento do co-design de hardware-software para otimizar o desempenho do QEC. À medida que o hardware quântico amadurece, o ecossistema deve observar uma colaboração crescente entre fabricantes de hardware, desenvolvedores de sistemas de controle e especialistas em algoritmos quânticos, acelerando o caminho em direção à computação quântica comercialmente viável e corrigida por erros.

Tamanho do Mercado, Previsões de Crescimento e CAGR (2025–2030)

O mercado de hardware de correção de erros quânticos (QEC) está posicionado para uma expansão significativa à medida que a computação quântica transita de pesquisas laboratoriais para implantações comerciais em estágio inicial. Em 2025, o mercado global de hardware de computação quântica é estimado em baixos bilhões de USD, com o hardware de QEC representando um subconjunto em rápido crescimento devido ao seu papel crítico na escalabilidade de processadores quânticos e na obtenção de tolerância a falhas. A demanda por hardware de QEC é impulsionada pela necessidade de mitigar a decoerência e erros operacionais em bits quânticos (qubits), o que é essencial para a computação quântica prática.

Principais players da indústria, como IBM, Intel, Rigetti Computing e Quantinuum estão desenvolvendo ativamente arquiteturas de hardware que integram QEC no nível de chip e sistema. Por exemplo, IBM se comprometeu publicamente a alcançar sistemas quânticos em larga escala e corrigidos por erros até o final da década de 2020, com seu roteiro de 2025 incluindo o deployment de qubits lógicos e correção de erros integrada no hardware. De forma semelhante, Rigetti Computing e Quantinuum estão avançando nas plataformas supercondutoras e de íons aprisionados, respectivamente, com foco em implementações de QEC escaláveis.

Previsões de crescimento para o segmento de hardware de QEC indicam uma taxa de crescimento anual composta (CAGR) superior a 30% entre 2025 e 2030, superando o mercado mais amplo de hardware quântico. Essa aceleração é atribuída tanto ao investimento público quanto privado em infraestrutura quântica, bem como ao reconhecimento crescente de que uma correção de erros robusta é um pré-requisito para a vantagem quântica comercial. Espera-se que o mercado alcance vários bilhões de USD até 2030, com o hardware de QEC representando uma parcela substancial à medida que mais processadores quânticos transitem de dispositivos quânticos de escala intermediária ruidosa (NISQ) para arquiteturas corrigidas por erros.

Além dos jogadores estabelecidos, startups e fornecedores de hardware especializados estão entrando no ecossistema de QEC, desenvolvendo controladores criogênicos, sistemas de leitura de alta fidelidade e chipsets personalizados de correção de erros. Empresas como Quantinuum e Rigetti Computing também estão colaborando com parceiros acadêmicos e governamentais para acelerar a comercialização do hardware de QEC.

Olhando para o futuro, os próximos anos verão uma maior integração do hardware de QEC nas plataformas de computação quântica, com implantações piloto em serviços quânticos acessíveis na nuvem e aplicações empresariais iniciais. À medida que a tecnologia amadurecer, espera-se que o mercado de hardware de QEC se torne um pilar central da indústria de computação quântica, sustentando a transição para máquinas quânticas tolerantes a falhas.

Principais Jogadores e Iniciativas da Indústria (IBM, Google, Rigetti, IonQ, Quantinuum)

O hardware de correção de erros quânticos (QEC) é um foco central para as principais empresas de computação quântica enquanto buscam alcançar a computação quântica tolerante a falhas. Em 2025, o campo está testemunhando avanços rápidos, com players-chave como IBM, Google, Rigetti Computing, IonQ e Quantinuum liderando tanto a pesquisa quanto o desenvolvimento de hardware.

IBM continua a liderar com sua tecnologia de qubit supercondutor, focando em aumentar o número de qubits físicos e integrar protocolos de QEC diretamente no hardware. Em 2024, a IBM demonstrou a correção de erros em tempo real em seu processador Eagle, e até 2025, espera-se que implemente qubits lógicos com correção de erros ativa em seus sistemas de próxima geração. O roteiro da IBM inclui o desenvolvimento de processadores quânticos modulares, projetados para suportar a correção de erros por código de superfície e facilitar a construção de qubits lógicos com taxas de erro mais baixas.

Google está avançando sua arquitetura Sycamore, enfatizando a implementação de QEC com código de superfície. Nos últimos anos, o Google demonstrou a estabilização de qubits lógicos e a extensão dos tempos de vida dos qubits usando correção de erros embutida no hardware. O foco da empresa para 2025 está em aumentar o número de qubits lógicos corrigidos por erros e reduzir as sobrecargas necessárias para o QEC, com o objetivo de alcançar uma tolerância a falhas prática em um futuro próximo.

Rigetti Computing também está perseguindo a tecnologia de qubit supercondutor, com uma ênfase particular em esquemas de QEC eficientes em hardware. Os processadores da série Aspen da Rigetti estão sendo atualizados para suportar a detecção e correção de erros em tempo real, aproveitando melhorias na conectividade dos qubits e na fidelidade de leitura. A empresa está colaborando com instituições de pesquisa para otimizar códigos de QEC para seu hardware, visando demonstrar qubits lógicos com taxas de erro competitivas até 2025.

IonQ utiliza a tecnologia de íons aprisionados, que oferece tempos de coerência inerentemente longos e operações de porta de alta fidelidade—vantagens-chave para QEC. A IonQ está desenvolvendo arquiteturas de hardware que suportam a implementação de qubits lógicos em pequena escala e está trabalhando para escalar para códigos QEC maiores. O roteiro da empresa inclui a integração de feedback em tempo real e rastreamento de erros diretamente em sua pilha de hardware, com o objetivo de demonstrar qubits lógicos robustos nos próximos anos.

Quantinuum, formada a partir da fusão da Honeywell Quantum Solutions e da Cambridge Quantum, aproveita hardware de íons aprisionados e algoritmos avançados de QEC. Os processadores da série H da Quantinuum são projetados para suportar a implementação de códigos topológicos e correção de erros em tempo real. A empresa está colaborando ativamente com parceiros da indústria e acadêmicos para acelerar a implantação do QEC embutido em hardware, visando a demonstração de qubits lógicos tolerantes a falhas até 2025.

Olhando para o futuro, espera-se que esses líderes da indústria façam avanços significativos no hardware de QEC, com foco em aumentar a contagem de qubits lógicos, reduzir taxas de erro e integrar protocolos de correção de erros no nível do hardware. Seus esforços coletivos devem definir a trajetória do hardware de computação quântica nos próximos anos.

Tecnologias Centrais: Códigos de Superfície, Qubits Gato e Abordagens Topológicas

O hardware de correção de erros quânticos (QEC) é um habilitador crítico para escalar computadores quânticos além da era quântica de escala intermediária ruidosa (NISQ). Em 2025, o campo está testemunhando um progresso rápido na implementação de tecnologias centrais de QEC, particularmente códigos de superfície, qubits gato e abordagens topológicas. Esses métodos estão sendo desenvolvidos e testados ativamente por empresas líderes de hardware quântico, cada uma aproveitando plataformas físicas e estratégias de engenharia únicas.

Os códigos de superfície continuam sendo o esquema de QEC mais amplamente adotado devido aos seus limites de erro relativamente altos e à compatibilidade com matrizes de qubits bidimensionais. IBM demonstrou várias rodadas de correção de erros com código de superfície em seus processadores de qubits supercondutores, com marcos recentes incluindo tempos de vida de qubits lógicos que superam os dos qubits físicos. Google também relatou avanços significativos, alcançando baixas taxas de erro lógico e escalando o número de qubits físicos em seus dispositivos da classe Sycamore. Ambas as empresas estão visando a demonstração de qubits lógicos com taxas de erro abaixo do chamado ponto de “break-even”, uma etapa chave em direção à computação quântica tolerante a falhas.

Qubits gato, que codificam informação quântica em superposições de estados coerentes dentro de cavidades de micro-ondas, oferecem uma rota alternativa para QEC com potencialmente menor sobrecarga de hardware. Alice & Bob, uma startup francesa, está na vanguarda dessa abordagem, tendo demonstrado qubits gato eficientes em hardware com viés de erro embutido e autocorreção de erros. Seu roteiro inclui escalonar para qubits lógicos com taxas de erro competitivas com implementações de código de superfície. Quantinuum também está explorando códigos bosônicos e qubits gato, aproveitando seu hardware de íons aprisionados para experimentos de QEC flexíveis.

Abordagens topológicas, como aquelas baseadas em modos zero de Majorana, prometem proteção inerente contra ruídos locais. Quantinuum e Microsoft são jogadores notáveis nesse espaço. A Microsoft, em particular, investiu pesadamente no desenvolvimento de qubits topológicos usando nanofios semicondutores-supercondutores híbridos, com o objetivo de demonstrar estatísticas não abelianas e operações topologicamente protegidas. Embora os qubits topológicos práticos permaneçam na fase experimental, os recentes avanços em ciência dos materiais e fabricação de dispositivos estão acelerando o cronograma para possíveis demonstrações.

Olhando para o futuro, espera-se que os próximos anos tragam uma maior integração do hardware de QEC em processadores quânticos comerciais, com um foco em aumentar a fidelidade dos qubits lógicos e reduzir a sobrecarga de recursos. Colaborações entre plataformas e avanços na eletrônica de controle criogênico, como as buscadas por empresas como Rigetti Computing e QuTech, serão cruciais para escalar as arquiteturas de QEC. A corrida para alcançar uma correção de erros quânticos prática e eficiente em hardware está se intensificando, preparando o cenário para as primeiras demonstrações de algoritmos quânticos tolerantes a falhas até o final da década de 2020.

Arquiteturas de Hardware: Supercondutores, Íons Aprisionados e Plataformas Fotônicas

O hardware de correção de erros quânticos (QEC) é um habilitador crítico para escalar computadores quânticos além da era quântica de escala intermediária ruidosa (NISQ). Em 2025, as principais plataformas de hardware quântico—qubits supercondutores, íons aprisionados e sistemas fotônicos—estão todas ativamente desenvolvendo e implantando esquemas de QEC, com progresso significativo e desafios distintos para cada arquitetura.

Nos sistemas de qubits supercondutores, o hardware de QEC está avançando rapidamente, impulsionado pela necessidade de mitigar a decoerência e erros de porta. IBM demonstrou a operação de qubits lógicos pequenos usando correção de erros com código de superfície em seus mais recentes processadores quânticos, com melhorias de hardware como acopladores ajustáveis e leitura rápida e de alta fidelidade. Google também relatou progresso em escalar qubits lógicos, focando em aumentar o número de qubits físicos por qubit lógico e otimizar a eletrônica de controle criogênica. Ambas as empresas estão visando taxas de erro lógico abaixo das taxas de erro físico, um marco chave para a computação quântica tolerante a falhas. Rigetti Computing e Quantinuum estão investindo de forma semelhante em QEC a nível de hardware, com esforços para integrar feedback em tempo real e extração de síndromes diretamente em suas pilhas de controle.

As plataformas de íons aprisionados, lideradas por IonQ e Quantinuum, se beneficiam de tempos de coerência inerentemente longos e portas de alta fidelidade, que são vantajosas para QEC. Essas empresas demonstraram qubits lógicos em pequena escala e estão trabalhando em arquiteturas de hardware que suportam escalonamento modular e medição de síndromes eficiente. O uso de armadilhas segmentadas e interconexões fotônicas está sendo explorado para facilitar o paralelismo necessário para QEC em grande escala. Espera-se que os próximos anos vejam a implantação de matrizes maiores de qubits lógicos e a integração de rotinas de QEC em ofertas comerciais de nuvem quântica.

A computação quântica fotônica, representada por empresas como PsiQuantum e Xanadu Quantum Technologies, está perseguindo QEC de hardware através de códigos bosônicos e arquiteturas de estado de cluster. Essas abordagens aproveitam as propriedades únicas dos fótons, como baixo ruído e operação em temperatura ambiente, mas enfrentam desafios na geração determinística de fótons e correção de erros tolerante à perda. A PsiQuantum está desenvolvendo chips fotônicos de silício projetados para QEC em grande escala, visando uma arquitetura de um milhão de qubits físicos, enquanto a Xanadu está avançando protocolos de QEC de variáveis contínuas em seu hardware fotônico.

Em todas as plataformas, as perspectivas para 2025 e além estão focadas em aumentar o tamanho e a confiabilidade dos qubits lógicos, integrando QEC em sistemas de hardware e controle, e demonstrando tempos de vida de qubits lógicos estendidos. Espera-se que os próximos anos tragam demonstrações de hardware de qubits lógicos superando seus equivalentes físicos, um passo crucial rumo à computação quântica prática e tolerante a falhas.

Desafios de Integração: Escalabilidade, Fidelidade e Consumo de Energia

O hardware de correção de erros quânticos (QEC) está no cerne dos esforços para construir computadores quânticos escaláveis e tolerantes a falhas. À medida que o campo avança para 2025, três grandes desafios de integração dominam: escalabilidade, fidelidade e consumo de energia. Cada um apresenta obstáculos únicos para os desenvolvedores de hardware, moldando a trajetória da computação quântica no curto prazo.

Escalabilidade continua sendo um obstáculo central. Os processadores quânticos atuais, como os desenvolvidos pela IBM e Google, demonstraram dispositivos com mais de 100 qubits físicos, mas o QEC requer milhares—se não milhões—de qubits físicos para codificar um único qubit lógico com taxas de erro suficientemente baixas. O desafio não está apenas em fabricar grandes matrizes de qubits, mas também em integrar a complexa eletrônica de controle e leitura necessárias para a detecção e correção de erros em tempo real. Empresas como Intel estão explorando tecnologias de embalagem avançadas e interconexões, como integração 3D e chips de controle criogênicos, para abordar esses gargalos de escalabilidade.

Fidelidade—a precisão das operações quânticas—é outro fator crítico. Os protocolos de QEC exigem fidelidades de portas e medições bem acima de 99,9% para serem eficazes. Embora plataformas de qubits supercondutores da IBM e Google tenham relatado melhorias constantes, manter alta fidelidade em grandes matrizes de qubits densamente empacotados é um desafio formidável. Interferência, ruído térmico e defeitos materiais podem degradar o desempenho. Inovações em hardware, como acopladores ajustáveis e materiais de qubits aprimorados, estão sendo perseguidas para mitigar esses efeitos. Rigetti Computing e Delft Circuits estão entre aqueles que desenvolvem soluções de cabeamento e filtragem inovadoras para preservar a integridade do sinal em larga escala.

O consumo de energia é cada vez mais reconhecido como um fator limitante, especialmente à medida que os sistemas crescem. O hardware de QEC deve operar a temperaturas de milikelvins, exigindo refrigeradores de diluição e eletrônica criogênica especializada. A infraestrutura de controle para milhares de qubits pode consumir quilowatts de energia, muito do qual é dissipado como calor que deve ser removido do ambiente criogênico. A Intel e a IBM estão investindo em tecnologias de controle de baixa energia, como criocomputação CMOS, para reduzir a carga térmica e permitir sistemas maiores.

Olhando para o futuro, nos próximos anos, veremos inovações contínuas em materiais, arquiteturas de dispositivos e integração de sistemas. A corrida para demonstrar qubits lógicos com taxas de erro práticas impulsionará colaborações entre fabricantes de hardware, fornecedores de componentes e instituições de pesquisa. Superar esses desafios de integração é essencial para realizar a promessa da computação quântica em larga escala e tolerante a falhas.

Avanços Recentes e Demonstrações (2023–2025)

O hardware de correção de erros quânticos (QEC) viu avanços significativos entre 2023 e 2025, com várias empresas líderes de tecnologia quântica e instituições de pesquisa alcançando marcos notáveis. O foco tem sido demonstrar esquemas de correção de erros escaláveis e eficientes em hardware e integrá-los em processadores quânticos cada vez mais complexos.

Em 2023, IBM anunciou a bem-sucedida demonstração de um qubit lógico usando seu hardware quântico supercondutor, marcando um passo-chave em direção à computação quântica tolerante a falhas. Sua abordagem utilizou correção de erros com código de superfície, que codifica um qubit lógico em uma rede de qubits físicos, permitindo a detecção e correção de erros em tempo real. Esta demonstração foi realizada em seu processador “Eagle” de 127 qubits, e iterações subsequentes melhoraram a fidelidade e a estabilidade de qubits lógicos.

De maneira similar, Google relatou progresso na implementação de QEC em seus processadores da classe Sycamore. Em 2024, o Google demonstrou a supressão de taxas de erro lógico abaixo das taxas de erro físico pela primeira vez, um limite crítico para a computação quântica escalável. Seus experimentos utilizaram códigos de repetição e códigos de superfície, aproveitando melhorias na coerência do qubit e na fidelidade das portas. Esses resultados foram corroborados por publicações revisadas por pares e atualizações técnicas públicas da empresa.

No domínio dos íons aprisionados, IonQ e Quantinuum também mostraram correção de erros em nível de hardware. A Quantinuum, em particular, demonstrou o uso do código de Bacon-Shor em seus processadores de armadilha iônica da série H1, alcançando ciclos de detecção e correção de erros em tempo real. A conectividade total e as portas de alta fidelidade de seu hardware permitiram uma implementação mais eficiente dos códigos de QEC em comparação com algumas plataformas supercondutoras.

No front do hardware, avanços em eletrônicos de controle criogênico, materiais de qubit e circuitos de detecção de erros integrados foram relatados por empresas como Intel e Rigetti Computing. A Intel focalizou qubits de spin em silício, visando arquiteturas escaláveis com recursos de correção de erros integrados, enquanto a Rigetti demonstrou melhorias em acopladores ajustáveis e fidelidade de leitura, ambos essenciais para um QEC robusto.

Olhando para os próximos anos, a indústria espera uma maior integração do hardware de QEC em processadores quânticos comerciais, com um foco em reduzir sobrecargas e aumentar os tempos de vida dos qubits lógicos. A convergência de hardware melhorado, sistemas de feedback em tempo real e códigos de correção de erros avançados deve trazer a computação quântica tolerante a falhas mais próxima da realidade.

Roteiro de Comercialização: Do Laboratório à Implantação no Mercado

O hardware de correção de erros quânticos (QEC) está rapidamente transitando de protótipos acadêmicos para produtos comerciais, impulsionado pela urgente necessidade de escalar computadores quânticos além da era quântica de escala intermediária ruidosa (NISQ). Em 2025, o roteiro de comercialização para o hardware de QEC é moldado tanto por avanços tecnológicos quanto por investimentos estratégicos de empresas líderes de hardware quântico, com foco na integração da correção de erros em processadores quânticos práticos.

O principal desafio abordado pelo hardware de QEC é a fragilidade inerente dos bits quânticos (qubits), que são suscetíveis à decoerência e erros operacionais. Para alcançar uma computação quântica tolerante a falhas, o hardware deve suportar qubits lógicos—codificados através de muitos qubits físicos usando códigos de correção de erros como o código de superfície. Este requisito levou a um aumento na pesquisa e desenvolvimento de arquiteturas de qubits escaláveis e de baixo ruído, juntamente com eletrônicos de controle de apoio.

Em 2025, IBM continua a liderar na integração do hardware de QEC, tendo demonstrado qubits lógicos com taxas de erro abaixo do limite do código de superfície em suas plataformas supercondutoras. Seu roteiro inclui o deployment de processadores quânticos modulares com correção de erros integrada, visando a primeira demonstração de operações de qubits lógicos com tempos de vida superiores aos dos melhores qubits físicos. A abordagem da IBM aproveita eletrônica de controle criogênica avançada e eletrônicos de micro-ondas de alta fidelidade, com foco na ampliação para milhares de qubits físicos por qubit lógico.

Google também está avançando o hardware de QEC, com seus processadores Sycamore e subsequentes mirando a demonstração de qubits lógicos com taxas de erro adequadas para algoritmos práticos. Seus esforços incluem o desenvolvimento de hardware criogênico personalizado e sistemas de feedback rápido para permitir detecção e correção de erros em tempo real. O roteiro da Google antecipa as primeiras ofertas comerciais de serviços quânticos em nuvem corrigidos por erros dentro dos próximos anos, dependendo de melhorias contínuas na coerência do qubit e na fidelidade das portas.

Outros jogadores-chave incluem Rigetti Computing, que está desenvolvendo arquiteturas supercondutoras modulares com QEC integrado, e IonQ, que está explorando sistemas de íons aprisionados com conectividade total para facilitar a correção de erros eficiente. Ambas as empresas estão visando implantações comerciais de processadores quânticos habilitados para QEC para acesso em nuvem e aplicações especializadas até o final da década de 2020.

Olhando para o futuro, a comercialização do hardware de QEC dependerá de reduções adicionais nas taxas de erro de qubits físicos, melhorias na infraestrutura criogênica e de controle, e no desenvolvimento de arquiteturas escaláveis. Roteiros da indústria sugerem que, até o final da década de 2020, os primeiros computadores quânticos comerciais com correção de erros ativa estarão disponíveis, permitindo as primeiras aplicações quânticas tolerantes a falhas em campos como criptografia, ciência dos materiais e otimização.

Regulamentação, Padronização e Colaboração na Indústria (IEEE, QED-C)

O hardware de correção de erros quânticos (QEC) está rapidamente emergindo como uma área crítica de foco para a indústria de computação quântica, com esforços de regulamentação, padronização e colaboração se intensificando à medida que o campo se aproxima da implantação prática. Em 2025, a paisagem é moldada pela interação entre consórcios líderes da indústria, órgãos de padronização e fabricantes de hardware, todos com o objetivo de garantir interoperabilidade, confiabilidade e escalabilidade das soluções de QEC.

A IEEE assumiu um papel central na padronização de tecnologias quânticas, incluindo hardware de correção de erros. A Iniciativa Quântica da IEEE, através de seu Grupo de Trabalho de Padrões Quânticos, está desenvolvendo ativamente estruturas e diretrizes para interfaces de hardware de QEC, benchmarking e métricas de desempenho. Esses esforços são projetados para facilitar a compatibilidade entre plataformas e acelerar a adoção de QEC em processadores quânticos comerciais. Espera-se que os padrões da IEEE influenciem os requisitos de aquisição e regulamentação para hardware quântico nos próximos anos.

Outra força majoritária é o Consórcio de Desenvolvimento Econômico Quântico (QED-C), que reúne partes interessadas da indústria, academia e governo. O Comitê Consultivo Técnico de Hardware do QED-C está trabalhando para identificar as melhores práticas e padrões pré-competitivos para hardware de QEC, focando em taxas de erro, limites de tolerância a falhas e integração com eletrônicas de controle. Os projetos colaborativos do consórcio em 2025 incluem benchmarking em rodízio de módulos de QEC e desenvolvimento de designs de referência abertos para circuitos de extração de síndromes.

Do lado do fabricante, empresas como IBM, Rigetti Computing e Quantinuum estão participando ativamente desses esforços de padronização. A IBM, por exemplo, contribuiu para a definição de protocolos de correção de erros e camadas de abstração de hardware, aproveitando sua experiência com arquiteturas de qubits supercondutores. A Rigetti está colaborando em padrões de co-design hardware-software, enquanto a Quantinuum está fornecendo contribuições com base em suas implementações de QEC com íons aprisionados. Essas empresas também estão testando a conformidade com os padrões emergentes em seus próximos processadores quânticos de próxima geração, visando demonstrar operação tolerante a falhas até o final da década de 2020.

Olhando para o futuro, espera-se que agências reguladoras nos EUA, UE e Ásia façam referência aos padrões da IEEE e do QED-C em suas orientações para aquisição e certificação de hardware quântico. Isso provavelmente impulsionará uma maior harmonização em toda a indústria, reduzirá a fragmentação e apoiará o desenvolvimento de uma cadeia de suprimentos robusta para componentes de QEC. À medida que o hardware de correção de erros quânticos transita de protótipos laboratoriais para implantação comercial, os esforços colaborativos de órgãos de padronização e consórcios da indústria serão fundamentais para garantir a confiabilidade e escalabilidade dos sistemas de computação quântica.

Perspectivas Futuras: Impacto na Computação Quântica e Aplicações da Indústria

O hardware de correção de erros quânticos (QEC) está prestes a desempenhar um papel transformador na evolução da computação quântica, particularmente à medida que a indústria se aproxima do limiar de sistemas quânticos práticos e tolerantes a falhas. Em 2025, os principais desenvolvedores de hardware quântico estão intensificando os esforços para integrar o QEC na camada física, com o objetivo de mitigar a decoerência e erros operacionais que atualmente limitam a escalabilidade e confiabilidade dos processadores quânticos.

Principais players, como IBM, Intel e Rigetti Computing, estão desenvolvendo ativamente arquiteturas de hardware que suportam qubits lógicos—um passo essencial para implementar códigos de QEC como o código de superfície. Em 2024, IBM demonstrou um processador Eagle de 127 qubits e delineou um roteiro rumo a operações quânticas corrigidas por erros, visando o deployment de qubits lógicos até 2025. A Intel está perseguindo qubits de spin em silício, aproveitando sua experiência na fabricação de semicondutores para melhorar a uniformidade dos qubits e taxas de erro, enquanto Rigetti Computing continua a refinar suas plataformas de qubits supercondutores com protocolos de QEC integrados.

Paralelamente, a inovação em hardware está sendo impulsionada por empresas especializadas em eletrônicos de controle criogênico e interconexões escaláveis, como Teledyne Technologies e Rohde & Schwarz. Essas empresas estão desenvolvendo sistemas de geração de sinal e leitura de alta fidelidade, que são críticos para os loops de feedback em tempo real exigidos pelo QEC. Além disso, Quantinuum (formada pela fusão das soluções quânticas da Honeywell e da Cambridge Quantum) está avançando com hardware de íons aprisionados com correção de erros integrada, recentemente demonstrando operações de qubits lógicos com tempos de vida e fidelidades de porta melhoradas.

Olhando para os próximos anos, espera-se que a indústria antecipe as primeiras demonstrações de cálculos quânticos tolerantes a falhas em pequena escala usando qubits lógicos protegidos por hardware de QEC. Esse marco deve desbloquear novas aplicações da indústria, particularmente em campos que exigem simulações de alta precisão, como farmacêuticos, ciência dos materiais e criptografia. A transição de dispositivos quânticos de escala intermediária ruidosa (NISQ) para processadores quânticos corrigidos por erros também catalisará o desenvolvimento de serviços quânticos em nuvem, à medida que fornecedores como IBM e Quantinuum se preparam para oferecer acesso a qubits lógicos para usuários comerciais e de pesquisa.

Em resumo, 2025 marca um ano crucial para o hardware de QEC, com progressos significativos esperados na integração da correção de erros no nível do dispositivo. As melhorias resultantes na fidelidade dos qubits e na confiabilidade computacional estão destinadas a acelerar a adoção da computação quântica em uma variedade de indústrias, estabelecendo as bases para as primeiras aplicações quânticas práticas e em larga escala.

Fontes e Referências

- IBM

- Rigetti Computing

- Quantinuum

- Qblox

- IonQ

- Alice & Bob

- Quantinuum

- Microsoft

- Xanadu Quantum Technologies

- IBM

- Rigetti Computing

- IonQ

- Quantinuum

- IEEE

- Consórcio de Desenvolvimento Econômico Quântico (QED-C)

- Teledyne Technologies

- Rohde & Schwarz