Quantum Error Correction Hardware in 2025: The Critical Leap Toward Fault-Tolerant Quantum Computing. Explore How Next-Gen Hardware is Shaping the Future of Quantum Reliability and Commercialization.

- Executive Summary: Quantum Error Correction Hardware Landscape 2025

- Market Size, Growth Forecasts, and CAGR (2025–2030)

- Key Players and Industry Initiatives (IBM, Google, Rigetti, IonQ, Quantinuum)

- Core Technologies: Surface Codes, Cat Qubits, and Topological Approaches

- Hardware Architectures: Superconducting, Trapped Ion, and Photonic Platforms

- Integration Challenges: Scalability, Fidelity, and Power Consumption

- Recent Breakthroughs and Demonstrations (2023–2025)

- Commercialization Roadmap: From Lab to Market Deployment

- Regulatory, Standardization, and Industry Collaboration (IEEE, QED-C)

- Future Outlook: Impact on Quantum Computing and Industry Applications

- Sources & References

Executive Summary: Quantum Error Correction Hardware Landscape 2025

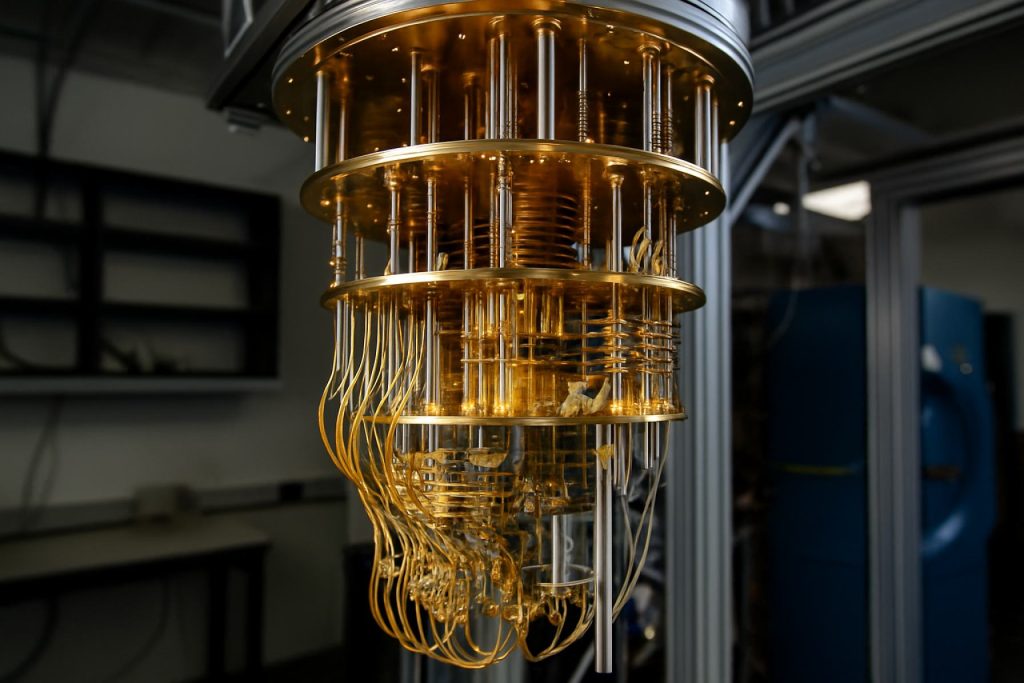

Quantum error correction (QEC) hardware is rapidly emerging as a critical enabler for the next generation of quantum computers, addressing the fundamental challenge of qubit decoherence and operational errors. As of 2025, the landscape is defined by a convergence of advanced materials, novel qubit architectures, and integrated control systems, with leading quantum hardware companies accelerating the transition from laboratory demonstrations to scalable, fault-tolerant quantum processors.

The field is dominated by a handful of major players, each pursuing distinct hardware strategies. IBM continues to advance its superconducting qubit roadmap, with its 2025 systems incorporating hardware-efficient surface code implementations and cryogenic control electronics designed to support logical qubits. Google is similarly focused on superconducting circuits, having demonstrated small-scale surface code patches and targeting the realization of logical qubits with error rates below the so-called “break-even” threshold. Rigetti Computing and Quantinuum (a merger of Honeywell Quantum Solutions and Cambridge Quantum) are also pushing the boundaries of error-corrected quantum hardware, with Quantinuum leveraging trapped-ion technology to implement real-time QEC cycles and demonstrate logical qubit lifetimes exceeding those of physical qubits.

In parallel, PsiQuantum is pursuing a photonic approach, aiming to leverage silicon photonics and integrated error correction to achieve large-scale, fault-tolerant quantum computing. Their hardware roadmap emphasizes the integration of error correction at the chip level, with a focus on manufacturability and scalability. Delft Circuits and Qblox are notable for their development of cryogenic and room-temperature control hardware, which is essential for the real-time feedback and low-latency operations required by QEC protocols.

Industry-wide, 2025 is expected to see the first demonstrations of logical qubits with lifetimes and fidelities surpassing those of their constituent physical qubits, a milestone that will validate the practical utility of QEC hardware. The outlook for the next few years includes the scaling of logical qubit arrays, the integration of classical co-processors for error decoding, and the refinement of hardware-software co-design to optimize QEC performance. As quantum hardware matures, the ecosystem is likely to see increased collaboration between hardware manufacturers, control system developers, and quantum algorithm specialists, accelerating the path toward commercially viable, error-corrected quantum computing.

Market Size, Growth Forecasts, and CAGR (2025–2030)

The market for quantum error correction (QEC) hardware is poised for significant expansion as quantum computing transitions from laboratory research to early-stage commercial deployment. As of 2025, the global quantum computing hardware market is estimated to be in the low single-digit billions of USD, with QEC hardware representing a rapidly growing subset due to its critical role in scaling quantum processors and achieving fault tolerance. The demand for QEC hardware is driven by the need to mitigate decoherence and operational errors in quantum bits (qubits), which is essential for practical quantum computation.

Key industry players such as IBM, Intel, Rigetti Computing, and Quantinuum are actively developing hardware architectures that integrate QEC at the chip and system level. For instance, IBM has publicly committed to achieving large-scale, error-corrected quantum systems by the late 2020s, with its 2025 roadmap including the deployment of logical qubits and hardware-embedded error correction. Similarly, Rigetti Computing and Quantinuum are advancing superconducting and trapped-ion platforms, respectively, with a focus on scalable QEC implementations.

Growth forecasts for the QEC hardware segment indicate a compound annual growth rate (CAGR) exceeding 30% between 2025 and 2030, outpacing the broader quantum hardware market. This acceleration is attributed to both public and private investment in quantum infrastructure, as well as the increasing recognition that robust error correction is a prerequisite for commercial quantum advantage. The market is expected to reach several billion USD by 2030, with QEC hardware comprising a substantial share as more quantum processors transition from noisy intermediate-scale quantum (NISQ) devices to error-corrected architectures.

In addition to established players, startups and specialized hardware suppliers are entering the QEC ecosystem, developing cryogenic controllers, high-fidelity readout systems, and custom error-correcting chipsets. Companies such as Quantinuum and Rigetti Computing are also collaborating with academic and government partners to accelerate the commercialization of QEC hardware.

Looking ahead, the next few years will see increased integration of QEC hardware into quantum computing platforms, with pilot deployments in cloud-accessible quantum services and early enterprise applications. As the technology matures, the QEC hardware market is expected to become a central pillar of the quantum computing industry, underpinning the transition to fault-tolerant quantum machines.

Key Players and Industry Initiatives (IBM, Google, Rigetti, IonQ, Quantinuum)

Quantum error correction (QEC) hardware is a central focus for leading quantum computing companies as they strive to achieve fault-tolerant quantum computation. In 2025, the field is witnessing rapid advancements, with key players such as IBM, Google, Rigetti Computing, IonQ, and Quantinuum spearheading both research and hardware development.

IBM continues to lead with its superconducting qubit technology, focusing on scaling up the number of physical qubits and integrating QEC protocols directly into hardware. In 2024, IBM demonstrated real-time error correction on its Eagle processor, and by 2025, it is expected to deploy logical qubits with active error correction in its next-generation systems. IBM’s roadmap includes the development of modular quantum processors, which are designed to support surface code error correction and facilitate the construction of logical qubits with lower error rates.

Google is advancing its Sycamore architecture, emphasizing the implementation of surface code QEC. In recent years, Google has demonstrated the stabilization of logical qubits and the extension of qubit lifetimes using hardware-embedded error correction. The company’s focus for 2025 is on scaling up the number of error-corrected logical qubits and reducing the overhead required for QEC, with the goal of achieving practical fault tolerance in the near future.

Rigetti Computing is also pursuing superconducting qubit technology, with a particular emphasis on hardware-efficient QEC schemes. Rigetti’s Aspen series processors are being upgraded to support real-time error detection and correction, leveraging improvements in qubit connectivity and readout fidelity. The company is collaborating with research institutions to optimize QEC codes for its hardware, aiming to demonstrate logical qubits with competitive error rates by 2025.

IonQ utilizes trapped ion technology, which offers inherently long coherence times and high-fidelity gate operations—key advantages for QEC. IonQ is developing hardware architectures that support the implementation of small-scale logical qubits and is working towards scaling up to larger QEC codes. The company’s roadmap includes the integration of real-time feedback and error tracking directly into its hardware stack, with the aim of demonstrating robust logical qubits in the coming years.

Quantinuum, formed from the merger of Honeywell Quantum Solutions and Cambridge Quantum, leverages trapped ion hardware and advanced QEC algorithms. Quantinuum’s H-Series processors are designed to support the implementation of topological codes and real-time error correction. The company is actively collaborating with industry and academic partners to accelerate the deployment of hardware-embedded QEC, targeting the demonstration of fault-tolerant logical qubits by 2025.

Looking ahead, these industry leaders are expected to make significant strides in QEC hardware, with a focus on increasing logical qubit counts, reducing error rates, and integrating error correction protocols at the hardware level. Their collective efforts are likely to define the trajectory of quantum computing hardware over the next several years.

Core Technologies: Surface Codes, Cat Qubits, and Topological Approaches

Quantum error correction (QEC) hardware is a critical enabler for scaling quantum computers beyond the noisy intermediate-scale quantum (NISQ) era. As of 2025, the field is witnessing rapid progress in the implementation of core QEC technologies, particularly surface codes, cat qubits, and topological approaches. These methods are being actively developed and tested by leading quantum hardware companies, each leveraging unique physical platforms and engineering strategies.

Surface codes remain the most widely adopted QEC scheme due to their relatively high error thresholds and compatibility with two-dimensional qubit arrays. IBM has demonstrated repeated rounds of surface code error correction on its superconducting qubit processors, with recent milestones including logical qubit lifetimes surpassing those of physical qubits. Google has also reported significant advances, achieving low logical error rates and scaling up the number of physical qubits in their Sycamore-class devices. Both companies are targeting the demonstration of logical qubits with error rates below the so-called “break-even” point, a key step toward fault-tolerant quantum computation.

Cat qubits, which encode quantum information in superpositions of coherent states within microwave cavities, offer an alternative route to QEC with potentially lower hardware overhead. Alice & Bob, a French startup, is at the forefront of this approach, having demonstrated hardware-efficient cat qubits with built-in error bias and autonomous error correction. Their roadmap includes scaling up to logical qubits with error rates competitive with surface code implementations. Quantinuum is also exploring bosonic codes and cat qubits, leveraging their trapped-ion hardware for flexible QEC experiments.

Topological approaches, such as those based on Majorana zero modes, promise inherent protection against local noise. Quantinuum and Microsoft are notable players in this space. Microsoft, in particular, has invested heavily in the development of topological qubits using hybrid semiconductor-superconductor nanowires, with the goal of demonstrating non-Abelian statistics and topologically protected operations. While practical topological qubits remain in the experimental stage, recent progress in material science and device fabrication is accelerating the timeline for potential demonstrations.

Looking ahead, the next few years are expected to bring further integration of QEC hardware into commercial quantum processors, with a focus on increasing logical qubit fidelity and reducing resource overhead. Cross-platform collaborations and advances in cryogenic control electronics, as pursued by companies like Rigetti Computing and QuTech, will be crucial for scaling up QEC architectures. The race to achieve practical, hardware-efficient quantum error correction is intensifying, setting the stage for the first demonstrations of fault-tolerant quantum algorithms by the late 2020s.

Hardware Architectures: Superconducting, Trapped Ion, and Photonic Platforms

Quantum error correction (QEC) hardware is a critical enabler for scaling quantum computers beyond the noisy intermediate-scale quantum (NISQ) era. As of 2025, leading quantum hardware platforms—superconducting qubits, trapped ions, and photonic systems—are all actively developing and deploying QEC schemes, with significant progress and distinct challenges for each architecture.

In superconducting qubit systems, QEC hardware is advancing rapidly, driven by the need to mitigate decoherence and gate errors. IBM has demonstrated the operation of small logical qubits using surface code error correction on their latest quantum processors, with hardware improvements such as tunable couplers and fast, high-fidelity readout. Google has also reported progress in scaling up logical qubits, focusing on increasing the number of physical qubits per logical qubit and optimizing cryogenic control electronics. Both companies are targeting logical error rates below the physical error rates, a key milestone for fault-tolerant quantum computing. Rigetti Computing and Quantinuum are similarly investing in hardware-level QEC, with efforts to integrate real-time feedback and syndrome extraction directly into their control stacks.

Trapped ion platforms, led by IonQ and Quantinuum, benefit from inherently long coherence times and high-fidelity gates, which are advantageous for QEC. These companies have demonstrated small-scale logical qubits and are working on hardware architectures that support modular scaling and efficient syndrome measurement. The use of segmented traps and photonic interconnects is being explored to facilitate the parallelism required for large-scale QEC. The next few years are expected to see the deployment of larger logical qubit arrays and the integration of QEC routines into commercial quantum cloud offerings.

Photonic quantum computing, represented by companies such as PsiQuantum and Xanadu Quantum Technologies, is pursuing hardware QEC through bosonic codes and cluster-state architectures. These approaches leverage the unique properties of photons, such as low noise and room-temperature operation, but face challenges in deterministic photon generation and loss-tolerant error correction. PsiQuantum is developing silicon photonic chips designed for large-scale QEC, aiming for a million-physical-qubit architecture, while Xanadu is advancing continuous-variable QEC protocols in their photonic hardware.

Across all platforms, the outlook for 2025 and beyond is focused on increasing the size and reliability of logical qubits, integrating QEC into hardware and control systems, and demonstrating extended logical qubit lifetimes. The next few years are expected to bring hardware demonstrations of logical qubits outperforming their physical counterparts, a crucial step toward practical, fault-tolerant quantum computing.

Integration Challenges: Scalability, Fidelity, and Power Consumption

Quantum error correction (QEC) hardware is at the heart of efforts to build scalable, fault-tolerant quantum computers. As the field moves into 2025, three major integration challenges dominate: scalability, fidelity, and power consumption. Each presents unique obstacles for hardware developers, shaping the trajectory of quantum computing in the near term.

Scalability remains a central hurdle. Current quantum processors, such as those developed by IBM and Google, have demonstrated devices with over 100 physical qubits, but QEC requires thousands—if not millions—of physical qubits to encode a single logical qubit with sufficiently low error rates. The challenge is not only in fabricating large arrays of qubits, but also in integrating the complex control and readout electronics required for real-time error detection and correction. Companies like Intel are exploring advanced packaging and interconnect technologies, such as 3D integration and cryogenic control chips, to address these scaling bottlenecks.

Fidelity—the accuracy of quantum operations—is another critical factor. QEC protocols demand gate and measurement fidelities well above 99.9% to be effective. While superconducting qubit platforms from IBM and Google have reported steady improvements, maintaining high fidelity across large, densely packed qubit arrays is a formidable challenge. Crosstalk, thermal noise, and material defects can all degrade performance. Hardware innovations, such as tunable couplers and improved qubit materials, are being pursued to mitigate these effects. Rigetti Computing and Delft Circuits are among those developing novel wiring and filtering solutions to preserve signal integrity at scale.

Power consumption is increasingly recognized as a limiting factor, especially as systems grow. QEC hardware must operate at millikelvin temperatures, requiring dilution refrigerators and specialized cryogenic electronics. The control infrastructure for thousands of qubits can consume kilowatts of power, much of it dissipated as heat that must be removed from the cryogenic environment. Intel and IBM are investing in cryo-CMOS and other low-power control technologies to reduce the thermal load and enable larger systems.

Looking ahead, the next few years will see continued innovation in materials, device architectures, and system integration. The race to demonstrate logical qubits with practical error rates will drive collaborations between hardware manufacturers, component suppliers, and research institutions. Overcoming these integration challenges is essential for realizing the promise of large-scale, fault-tolerant quantum computing.

Recent Breakthroughs and Demonstrations (2023–2025)

Quantum error correction (QEC) hardware has seen significant advances between 2023 and 2025, with several leading quantum technology companies and research institutions achieving notable milestones. The focus has been on demonstrating scalable, hardware-efficient error correction schemes and integrating them into increasingly complex quantum processors.

In 2023, IBM announced the successful demonstration of a logical qubit using their superconducting quantum hardware, marking a key step toward fault-tolerant quantum computing. Their approach utilized surface code error correction, which encodes a logical qubit into a lattice of physical qubits, allowing for the detection and correction of errors in real time. This demonstration was performed on their 127-qubit “Eagle” processor, and subsequent iterations have improved the fidelity and stability of logical qubits.

Similarly, Google has reported progress in implementing QEC on their Sycamore-class processors. In 2024, Google demonstrated the suppression of logical error rates below the physical error rates for the first time, a critical threshold for scalable quantum computing. Their experiments used repetition codes and surface codes, leveraging improvements in qubit coherence and gate fidelity. These results have been corroborated by peer-reviewed publications and public technical updates from the company.

In the trapped-ion domain, IonQ and Quantinuum have both showcased hardware-level error correction. Quantinuum, in particular, demonstrated the use of the Bacon-Shor code on their H1 series ion-trap processors, achieving real-time error detection and correction cycles. Their hardware’s all-to-all connectivity and high-fidelity gates have enabled more efficient implementation of QEC codes compared to some superconducting platforms.

On the hardware front, advances in cryogenic control electronics, qubit materials, and integrated error detection circuits have been reported by companies such as Intel and Rigetti Computing. Intel has focused on silicon spin qubits, aiming for scalable architectures with built-in error correction features, while Rigetti has demonstrated improvements in tunable couplers and readout fidelity, both essential for robust QEC.

Looking ahead to the next few years, the industry expects further integration of QEC hardware into commercial quantum processors, with a focus on reducing overhead and increasing logical qubit lifetimes. The convergence of improved hardware, real-time feedback systems, and advanced error correction codes is anticipated to bring practical fault-tolerant quantum computing closer to reality.

Commercialization Roadmap: From Lab to Market Deployment

Quantum error correction (QEC) hardware is rapidly transitioning from academic prototypes to commercial products, driven by the urgent need to scale quantum computers beyond the noisy intermediate-scale quantum (NISQ) era. As of 2025, the commercialization roadmap for QEC hardware is shaped by both technological advances and strategic investments from leading quantum hardware companies, with a focus on integrating error correction into practical quantum processors.

The primary challenge addressed by QEC hardware is the inherent fragility of quantum bits (qubits), which are susceptible to decoherence and operational errors. To achieve fault-tolerant quantum computation, hardware must support logical qubits—encoded across many physical qubits using error-correcting codes such as the surface code. This requirement has led to a surge in research and development of scalable, low-noise qubit architectures and supporting control electronics.

In 2025, IBM continues to lead in the integration of QEC hardware, having demonstrated logical qubits with error rates below the surface code threshold on their superconducting platforms. Their roadmap includes the deployment of modular quantum processors with built-in error correction, aiming for the first demonstration of logical qubit operations with lifetimes exceeding those of the best physical qubits. IBM’s approach leverages advanced cryogenic control hardware and high-fidelity microwave electronics, with a focus on scaling up to thousands of physical qubits per logical qubit.

Google is also advancing QEC hardware, with its Sycamore and subsequent processors targeting the demonstration of logical qubits with error rates suitable for practical algorithms. Their efforts include the development of custom cryogenic hardware and fast feedback systems to enable real-time error detection and correction. Google’s roadmap anticipates the first commercial offerings of error-corrected quantum cloud services within the next few years, contingent on continued improvements in qubit coherence and gate fidelity.

Other key players include Rigetti Computing, which is developing modular superconducting architectures with integrated QEC, and IonQ, which is exploring trapped-ion systems with all-to-all connectivity to facilitate efficient error correction. Both companies are targeting commercial deployments of QEC-enabled quantum processors for cloud access and specialized applications by the late 2020s.

Looking ahead, the commercialization of QEC hardware will depend on further reductions in physical qubit error rates, improvements in cryogenic and control infrastructure, and the development of scalable architectures. Industry roadmaps suggest that by the late 2020s, early commercial quantum computers with active error correction will become available, enabling the first fault-tolerant quantum applications in fields such as cryptography, materials science, and optimization.

Regulatory, Standardization, and Industry Collaboration (IEEE, QED-C)

Quantum error correction (QEC) hardware is rapidly emerging as a critical focus area for the quantum computing industry, with regulatory, standardization, and collaborative efforts intensifying as the field approaches practical deployment. In 2025, the landscape is shaped by the interplay between leading industry consortia, standards bodies, and hardware manufacturers, all aiming to ensure interoperability, reliability, and scalability of QEC solutions.

The IEEE has taken a central role in standardizing quantum technologies, including error correction hardware. The IEEE Quantum Initiative, through its Quantum Standards Working Group, is actively developing frameworks and guidelines for QEC hardware interfaces, benchmarking, and performance metrics. These efforts are designed to facilitate cross-platform compatibility and accelerate the adoption of QEC in commercial quantum processors. The IEEE’s standards are expected to influence procurement and regulatory requirements for quantum hardware in the coming years.

Another major force is the Quantum Economic Development Consortium (QED-C), which brings together stakeholders from industry, academia, and government. QED-C’s Hardware Technical Advisory Committee is working to identify best practices and pre-competitive standards for QEC hardware, focusing on error rates, fault-tolerance thresholds, and integration with control electronics. The consortium’s collaborative projects in 2025 include round-robin benchmarking of QEC modules and the development of open reference designs for syndrome extraction circuits.

On the manufacturer side, companies such as IBM, Rigetti Computing, and Quantinuum are actively participating in these standardization efforts. IBM, for example, has contributed to the definition of error correction protocols and hardware abstraction layers, leveraging its experience with superconducting qubit architectures. Rigetti is collaborating on hardware-software co-design standards, while Quantinuum is providing input based on its trapped-ion QEC implementations. These companies are also piloting compliance with emerging standards in their next-generation quantum processors, aiming to demonstrate fault-tolerant operation by the late 2020s.

Looking ahead, regulatory agencies in the US, EU, and Asia are expected to reference IEEE and QED-C standards in their guidance for quantum hardware procurement and certification. This will likely drive further harmonization across the industry, reduce fragmentation, and support the development of a robust supply chain for QEC components. As quantum error correction hardware moves from laboratory prototypes to commercial deployment, the collaborative efforts of standards bodies and industry consortia will be pivotal in ensuring the reliability and scalability of quantum computing systems.

Future Outlook: Impact on Quantum Computing and Industry Applications

Quantum error correction (QEC) hardware is poised to play a transformative role in the evolution of quantum computing, particularly as the industry approaches the threshold of practical, fault-tolerant quantum systems. As of 2025, leading quantum hardware developers are intensifying efforts to integrate QEC at the physical layer, with the goal of mitigating decoherence and operational errors that currently limit the scalability and reliability of quantum processors.

Major players such as IBM, Intel, and Rigetti Computing are actively developing hardware architectures that support logical qubits—an essential step for implementing QEC codes like the surface code. In 2024, IBM demonstrated a 127-qubit Eagle processor and outlined a roadmap toward error-corrected quantum operations, targeting the deployment of logical qubits by 2025. Intel is pursuing silicon spin qubits, leveraging its semiconductor fabrication expertise to improve qubit uniformity and error rates, while Rigetti Computing continues to refine its superconducting qubit platforms with integrated QEC protocols.

In parallel, hardware innovation is being driven by companies specializing in cryogenic control electronics and scalable interconnects, such as Teledyne Technologies and Rohde & Schwarz. These firms are developing high-fidelity signal generation and readout systems, which are critical for the real-time feedback loops required by QEC. Additionally, Quantinuum (formed from the merger of Honeywell Quantum Solutions and Cambridge Quantum) is advancing trapped-ion hardware with built-in error correction, recently demonstrating logical qubit operations with improved lifetimes and gate fidelities.

Looking ahead to the next few years, the industry anticipates the first demonstrations of small-scale, fault-tolerant quantum computations using logical qubits protected by QEC hardware. This milestone is expected to unlock new industry applications, particularly in fields requiring high-precision simulations, such as pharmaceuticals, materials science, and cryptography. The transition from noisy intermediate-scale quantum (NISQ) devices to error-corrected quantum processors will also catalyze the development of quantum cloud services, as providers like IBM and Quantinuum prepare to offer access to logical qubits for commercial and research users.

In summary, 2025 marks a pivotal year for QEC hardware, with significant progress expected in the integration of error correction at the device level. The resulting improvements in qubit fidelity and computational reliability are set to accelerate the adoption of quantum computing across a range of industries, laying the groundwork for the first practical, large-scale quantum applications.

Sources & References

- IBM

- Rigetti Computing

- Quantinuum

- Qblox

- IonQ

- Alice & Bob

- Quantinuum

- Microsoft

- Xanadu Quantum Technologies

- IBM

- Rigetti Computing

- IonQ

- Quantinuum

- IEEE

- Quantum Economic Development Consortium (QED-C)

- Teledyne Technologies

- Rohde & Schwarz